随着电子设备性能的不断提升,CPU作为其核心部件,其制造工艺也在不断进步。多层堆叠技术是提高CPU性能和集成度的重要技术之一。然而,在实现多层堆叠的过程中,工程师们面临着一系列挑战。本文将详细介绍CPU多层堆叠技术的实现原理,并探讨在融合过程中遇到的关键难题。

CPU多层堆叠技术概述

CPU多层堆叠技术,顾名思义,是指在制造过程中将多个CPU核心层叠在一起,以提高计算效率和减少芯片面积。与传统的平面制造工艺相比,这种技术可以大大提升晶体管的集成度,是现代高性能处理器发展的关键。

实现过程详解

设计阶段

在设计阶段,工程师需要通过3D建模技术创建多个CPU核心的虚拟模型。设计阶段的主要任务是确保每个核心的物理尺寸、电路设计以及互连结构的精确匹配。

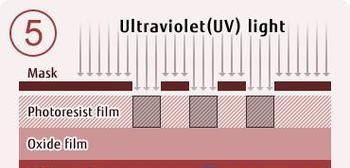

制造工艺

接下来是制造阶段。多层堆叠技术通常涉及硅穿孔(TSV)技术,它允许在垂直方向上穿过硅片并建立连接,从而形成堆叠结构。TSV技术是实现多层堆叠的基础,它的引入显著提高了互连的密度和性能。

封装技术

完成堆叠后,使用先进的微芯片封装技术将各个层整合封装在一起。封装技术不仅要保持各层的稳定性和互连的可靠性,还要确保散热和功耗在合理范围内。

面临的挑战

热管理

CPU核心工作时产生的热量是多层堆叠技术中的一个主要挑战。如何有效地从堆叠芯片中导热是确保性能稳定的关键。

信号完整性

随着堆叠层数的增加,信号传输路径变长,这对信号的完整性和时序提出了更高的要求。精确的电路设计和高级信号管理技术是解决这一问题的关键。

制造精度

在制造过程中,高精度的对准技术是实现各层之间成功互连的保障。任何微小的偏差都可能导致性能下降或设备故障。

高级话题拓展

晶圆级封装技术

晶圆级封装(WaferLevelPackaging,WLP)是一种与多层堆叠技术相辅相成的技术,它可以在晶圆制造阶段完成更多的封装工作,从而提高生产效率。

面向未来的创新技术

在探索CPU制造的未来方向时,一些新的概念如异质集成和光电集成正在逐渐浮现。这些技术有望解决现有挑战,并进一步提高CPU的性能和能效。

结语

多层堆叠技术是现代CPU制造领域的一项性进步,它在提升性能的同时也对制造工艺提出了更高的要求。尽管工程师们在热管理、信号完整性和制造精度等方面面临挑战,但通过不懈的努力和技术创新,这些问题正在逐步被克服。未来的CPU技术将向着更高集成度、更低功耗和更高性能的方向发展,为消费者带来更加强大和高效的计算体验。

标签: #cpu